Vol.26, No.3 June, 2011

## ·光电器件与材料·

# 界面电荷对 C-Si表面钝化质量的影响

高 华1,汪建强1,张 剑1,叶庆好2,孟凡英3

(1. 上海超日太阳能科技股份有限公司,上海 201406; 2. 上海交通大学 物理系太阳能研究所,上海 200240; 3. 中国科学院上海技术物理研究所,上海 200083)

摘 要:深入分析了影响晶体硅与钝化介质层界面复合的主要因素:界面态密度( $D_u$ )、介质层表面电荷密度、衬底掺杂类型及掺杂浓度。研究发现,随着载流子注入水平改变,介质层的钝化质量与介质层带电类型和硅片掺杂类型紧密相关。随着载流子注入水平的降低,富含正电荷(负电荷)的钝化介质在P型(N型)硅片上的钝化质量随之降低;富含负电荷(正电荷)的钝化介质在P型(N型)硅片上的钝化质量却保持不变。深入分析了P型(N型)掺杂硅片表面钝化质量随注入水平变化而产生不同变化的原因,并为高效晶体硅电池表面钝化提出指导性意见,对于工作在低注入水平条件下( $5 \times 10^{14}~{\rm cm}^{-3}$ )的晶体硅电池非常重要。

关键词:表面钝化质量;固定电荷;注入水平

中图分类号:TM914.4 文献标识码:A 文章编号:1673-1255(2011)03-0028-07

## Influence of Interface Charge on Passivation Quality of C-Si Surface

GAO Hua<sup>1</sup>, WANG Jian-qiang<sup>1</sup>, ZHANG Jian<sup>1</sup>, YE Qing-hao<sup>2</sup>, MENG Fan-ying<sup>3</sup>

(1. Shanghai Chaori Solar Energy Science & Technology Co., Ltd, Shanghai 201406, China;

- $2.\ Solar\ Energy\ Research\ Institute\ of\ Physics\ Department\ ,\ Shanghai\ Jiao\ Tong\ University\ ,\\ Shanghai\ \ 200240\ ,\ China\ ;$

- 3. Shanghai Institute of Technical Physics of the Chinese Academy of Science, Shanghai 200083, China)

**Abstract:** The main factors which influence the compound between the passivation medium layer and the crystalline silicon are analyzed, including the interface state density ( $D_u$ ), surface charge density of medium layer, doping type and doping concentration of the substrate. When the carrier injection level varies, the passivation quality is closely related to the charge type in medium layer and silicon doping type. As the carrier injection level decreases, the passivation quality of the passivation medium with positive charge on the P-type (N-type) silicon decreases, but the passivation quality of the passivation medium with negtive charge on the P-type (N-type) silicon still remains constant. The reason of the passivation quality varying with carriers injection level is analyzed. The guiding suggestion for the high effiency crystalline silicon cells is proposed, it is very important for silicon cells operating at low level injection level ( $5 \times 10^{14}$  cm<sup>-3</sup>).

Key words: surface passivation quality; fixed charge; injection level

1974年 M.A. Green 的 MIS(金属-绝缘体-半导体)<sup>[1]</sup>结构电池是第一块采用SiO<sub>2</sub>钝化的电池,第一块采用SiO<sub>2</sub>钝化的轻掺杂晶体硅电池获得了21%的电池效率<sup>[2]</sup>。晶体硅电池世界最高25%转换效率的PERL电池采用双面高温(1050°C)热二氧化硅钝

化,研究发现 FGA 退火以及蒸发铝层在  $N_2$  中退火能有效降低 $SiO_2/C$  – Si 界面复合中心密度 [3] ,且 $SiO_2$  薄膜中主要缺陷对电子和空穴的俘获截面有非常严重的不对称性,从而使得其在 P 型发射结和 N 型发射结上的钝化效果有所不同。高效晶体硅电池

收稿日期:2011-04-03

基金项目:上海市科委与应用材料联合基金(08520741400);上海市科委优秀学科带头人项目基金(08XD14022) 作者简介:高华(1982-),男,四川资阳人,工程师,研究方向为硅太阳电池技术.

C-Si(P)衬底上N型发射结表面钝化常用的是  $SiN_x(x>0)$ 薄膜,  $SiN_x$ 膜中有高密度的正电荷  $(1 \times 10^{12} \text{ cm}^{-2})$ 以及中等质量的SiN<sub>x</sub>/C - Si 界面态密 度  $D_{ii} = 1 \times 10^{11} \text{ cm}^{-2} \text{eV}^{-1}$ ,  $\text{SiN}_{x}$ 中的固定电荷密度随 着薄膜中Si含量的降低而降低,由于富含Si的SiN。 薄膜与C-Si界面质量的提高,通常高折射率的SiN。 薄膜有非常好的钝化效果,但其高折射率却无法满 足发射结表面减反射的要求。Al<sub>2</sub>O<sub>3</sub>薄膜中富含高 密度负电荷,且FGA气氛中退火薄膜中负电荷的密 度能提升约两个数量级,研究发现Al<sub>2</sub>O<sub>3</sub>/C-Si界面 有一层薄SiO2,使得Al2O3/C-Si界面有高质量界面 态非常适合P型发射结表面钝化。对于高掺杂C-Si (P)表面,具有高密度负电荷的Al<sub>2</sub>O<sub>3</sub>薄膜钝化效果 要远优于表面带正电的钝化介质材料(热氧化SiO2 以及 $SiN_x$ )。在N型衬底上,采用30 nm  $Al_2O_3$ 钝化的 B掺杂P型发射结电池已经获得了高达23.2%<sup>[4]</sup>的 电池效率( $V_{oc} = 703.6 \,\text{mV}$ ,  $J_{oe} = 29 \,\text{fA/cm}^2$ )。

详细研究了影响晶体硅表面钝化质量的主要因素:晶体硅与钝化介质层的界面态密度(Du),介质层内高密度电荷引起的场钝化效应,以及它们在不同掺杂衬底上的钝化效果。低注入水平条件下,介质表面电荷对不同掺杂类型硅片表面钝化质量的影响不同:富含正电荷(负电荷)的钝化介质在P型(N型)硅片上的钝化质量随之降低;富含负电荷(正电荷)的钝化介质在P型/N型硅片上的表面钝化质量却保持不变,这对于提高介质层在硅片表面的钝化质量,尤其是对于在低注入条件下(5×10<sup>14</sup> cm<sup>-3</sup>)工作的晶体硅电池非常重要。文中结合高效晶体硅电池的主流钝化工艺SiO<sub>2</sub>,SiN<sub>x</sub>以及Al<sub>2</sub>O<sub>3</sub>深入分析了P型(N型)掺杂类型硅片表面钝化质量随注入水平变化而产生不同变化的原因。

## 1 影响晶体硅表面钝化的因素

#### 1.1 晶体硅表面复合速度的决定因素

由 Shockley-Read-Hall(SRH)复合理论,单能级 缺陷态复合速度 $R_{SRH}(n,p)$ (cm<sup>-3</sup>.s<sup>-1</sup>)为<sup>[5]</sup>

$$R_{SRH}(n,p) = \frac{np - n_i^2}{\frac{n + n_i e^{(E_t - E_i)/KT}}{\delta_p} + \frac{p + n_i e^{-(E_t - E_i)/KT}}{\delta_n}} \nu_{th} N_t$$

(1)

式中, $N_t$ (cm<sup>-3</sup>)为缺陷态密度; $\delta p$  和 $\delta_n$ (cm<sup>2</sup>)为缺陷对空穴和电子的俘获截面。当 $n \times \delta_n = p \times \delta_p$ 条件满足,且缺陷态能级 $E_t$ 接近硅本征能级 $E_i$ (eV)时,此时复合中心能最有效地俘获载流子,从而有最差的钝化效果。与载流子注入水平相关,且有 2 种带电状态的表面缺陷态复合速率可以表示为

$$S_{SRH} (\Delta n_s) = \frac{1}{\Delta n} \times \frac{\left[ (n_0 + \Delta n_s)(p_0 + \Delta p_s) \right] - n_i^2}{(n_0 + \Delta n_s) + n_i e^{\frac{(E_t - E_i)/KT}{\delta}} + \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta_p}{\delta_n} (p_0 + \Delta p_s) + n_i e^{\frac{-(E_t - E_i)/KT}{\delta}} \times \frac{\delta$$

式中, $D_{ii}$ (cm<sup>-2</sup>)为界面缺陷态密度; $\Delta n_s$ 和 $\Delta p_s$ 分别为晶体硅与介质层界面过剩载流子浓度。

从式(2)可以看出,界面缺陷态对电子和空穴 俘获截面的比值( $\delta_n/\delta_p$ )严重影响晶体硅界面的复合速度。缺陷态的载流子俘获截面表征了复合中心对载流子复合的有效性,对于SiO<sub>2</sub>/C – Si 界面而言,SiO<sub>2</sub>介质中缺陷态对电子和空穴的俘获截面比值为: $\delta_n/\delta_p = 100^{[6,7]}$ 。正是由于SiO<sub>2</sub>介质层俘获截面的不对称性,以及其中等正电荷密度( $\approx 1 \times 10^{10}~{\rm cm}^{-2}$ )[8],从而在低注入水平条件下,SiO<sub>2</sub>在 C-Si(N)晶体硅衬底上的钝化质量要明显优于 C-Si(P)晶体硅衬底,这对于工作在注入水平为  $5 \times 10^{14}~{\rm cm}^{-3}$ ( $\approx$  One Sun)的晶体硅电池来说非常重要。晶体硅表面钝化介质的选择也成为高效晶体硅电池的重要因素。

经介质双面对称钝化的晶体硅与介质层界面有效复合速度 $(S_{eff})$ 可以表示为

$$S_{eff} = \left(\frac{1}{\tau_{eff}} - \frac{1}{\tau_{bulk}}\right) \times \frac{W}{2} \tag{3}$$

其中, $\tau_{bulk}$ 为晶体硅体寿命且可以表示为: $\frac{1}{\tau_{bulk}}$  =  $\frac{1}{\tau_{extr}}$  +  $\frac{1}{\tau_{intr}}$ ,  $\tau_{extr}$  为晶体硅材料中与缺陷相关的少子寿命; $\tau_{intr}$  为俄歇复合(Auger)和辐射复合相关的少子寿命。基于以上分析考虑,晶体硅与钝化层介质界面有效少子寿命可以表示为

$$\tau^{-1}_{eff} = \tau^{-1}_{bulk} + \frac{2}{W} \frac{1}{\Delta n} \times U_{DB}(\Delta n; n_0, p_0; Q_s, N_s; \delta_p, \delta_n)$$

(4)

降低晶体硅表面复合速度,可以从以下2个方面来考虑:(1)减少界面缺陷态密度 $(D_{ii})$ : 在整个过

剩载流子变化范围内, $U_{SRH}$ 始终正比于 $D_{ii}$ ;(2)减少界面电子或空穴的浓度:SRH复合需要电子空穴对的参与,当电子和空穴浓度满足: $n \times \delta_n = p \times \delta_p$ 时,有最大界面复合速度。由于电子和空穴都带电,技术上讲通过实现掺杂曲线或在晶体硅表面覆盖场效应钝化层,能在晶体硅和介质层界面引入内建电场,可以实现其中一种载流子的耗尽和另一种载流子的聚集,从而有效降低界面复合速率。

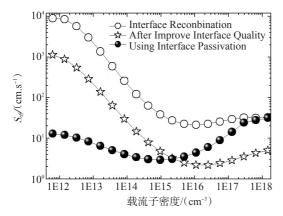

图1是介质层和晶体硅界面态密度以及介质层 钝化效果对界面复合速度的影响随载流子注入水平的依赖关系。可以看出,在载流子低注入条件下,场钝化效果的改进相对于提高晶体硅表面界面质量更能有效降低界面复合速度;随着载流子注入水平的增加,硅片表面的电荷随之逐渐减小并趋近于零。从而在高注入条件下,提高介质和晶体硅的界面态密度成为首要考虑因素。

图1 界面态密度和表面场钝化对界面复合速度的影响

#### 1.2 晶体硅表面电势( $\phi_s$ )的计算

晶体硅表面场效应钝化使得 $\Delta n_s \neq \Delta p_s$ ,表面有效复合速度为

$$S_{eff} = \frac{U_s}{\Delta n(x = d)} [\text{cm/s}]$$

(5)

其中,x=d 为晶体硅表面空间电荷区边界区域,晶体硅体内有: $\Delta n(x=d) = \Delta p(x=d)$ 。

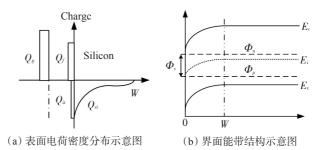

考虑晶体硅掺杂浓度以及体过剩载流子浓度  $(\Delta n = \Delta p)$ 对表面复合速度 $S_{eff}$ 的影响[9-11],引入了 "Extended SRH Formalism"机制计算了非平衡状态 条件下表面载流子浓度 $n_s$ 和 $p_s$ 。在一定表面电荷密度 $Q_s$ 下,其在晶体硅表面的诱导电荷为 $Q_{si}$ 。忽略表面空间电荷区内的复合,表面固定电荷具体可以表示为

$$Q_s = Q_{it} + Q_f + Q_G \tag{6}$$

其中, $Q_u$ 为界面缺陷态电荷密度; $Q_f$ 为表面介质层 (钝化层)中固定电荷密度; $Q_G$ 为介质层外加电荷。

图2 晶体硅表面电荷密度和界面能带结构图

界面缺陷态电荷密度可以表示为

$$Q_{ii} = -\int_{E_{V}}^{E_{C}} D_{ii,A}(E) \times f_{A}(E) dE + \int_{E_{V}}^{E_{C}} D_{ii,D}(E) \times f_{D}(E) dE$$

(7)

其中, $D_{u,A}(E)$ 和 $D_{u,D}(E)$ 为界面缺陷态受主和施主密度,受主缺陷态电子占据函数  $f_A(E)$ ,施主缺陷态空穴占据函数  $f_D(E)$ 可表示为

$$f_A(E) = \frac{\delta_n n_s + \delta_p n_i e^{-(E_t - E_i)/kT}}{\delta_n (n_s + n_i e^{(E_t - E_i)/kT}) + \delta_p (p_s + n_i e^{-(E_t - E_i)/kT})}$$

$$f_D(E) = \frac{\delta_p p_s + \delta_n n_i e^{(E_t - E_i)/kT}}{\delta_n (n_s + n_i e^{(E_t - E_i)/kT}) + \delta_p (p_s + n_i e^{-(E_t - E_i)/kT})}$$

(9)

晶体硅表面钝化介质层外表面电荷 $Q_c$ 可以通过法拉第定律推导

$$Q_G(\phi_s) = -\frac{1}{d_{ins}} [Q_f \frac{d_f}{2} + \frac{\varepsilon_0 \varepsilon_{ins}}{q} (\phi_s - V_G)]$$

(10)

其中, $V_G$ 为加在晶体硅表面介质层上的偏置电压; $d_f$ 为距离表面固定电荷的距离; $d_{ins}$ 为晶体硅表面介质层厚度; $\varepsilon_{ins}$ 为介质层的相对电容; $p_s$ 为表面电势  $\phi_s$ 决定了界面载流子浓度。

$$n_s = (n_0 + \Delta n)e^{(+^{q\phi} \cdot /_{kT})}$$

, $p_s = (p_0 + \Delta p)e^{(-^{q\phi} \cdot /_{kT})}$  (11)

晶体硅表面产生的诱导电荷可以表示为

$$Q_{Si} = -sign(\phi_s) \left\{ \frac{2kTn_i \,\varepsilon_0 \varepsilon_{Si}}{q^2} \left[ e^{q(\phi_p - \phi_s)/kT} - e^{q\phi_p/kT} + \right] \right\}$$

$$e^{\frac{q(\phi_{s}-\phi_{n})/kT}{kT}-e^{\frac{-q\phi_{n}/kT}{kT}}+\frac{q\phi_{s}(p_{0}-n_{0})}{kTn_{i}}]^{\frac{1}{2}}$$

(12)

其中, $\phi_n$ 和 $\phi_p$ 为空间电荷区边缘x=d 处电子和空穴的准费米能级

$$\phi_n = -(kT/q)\ln(\frac{n_0 + \Delta n}{n_i})$$

$$\phi_p = (kT/q)\ln(\frac{p_0 + \Delta n}{n_i})$$

$$\phi_s \approx \phi_n - \phi_p + E_{g,Si}$$

(13)

由式(13)可以看出 $Q_i$ 、 $Q_G$ 以及 $Q_s$ i都是 $n_s$ 、 $p_s$ 和 $\phi_s$ 的函数,由电中性条件

$$Q_{Si} + Q_S = Q_{Si} + Q_{it} + Q_f + Q_G = 0 (14)$$

$\phi_s$ 可以通过以上公式进行数值模拟计算得到, 当晶体硅和表面钝化介质层界面态密度 $(D_u)$ 非常小,同时在钝化层外表面没有外加电荷 $(Q_c=0)$ ,从 而上述电中性条件可以简化为

$$Q_S = Q_f = -Q_{Si} \tag{15}$$

从而上述非线性方程可以表示为

$$Q_{S} = -Q_{Si} = sign(\phi_{s}) \left\{ \frac{2kTn_{i} \varepsilon_{0} \varepsilon_{Si}}{q^{2}} \left[ e^{q(\phi_{p} - \phi_{s})/kT} - e^{q\phi_{p}/kT} + \frac{q\phi_{s}(p_{0} - n_{0})}{kTn_{i}} \right] \right\}^{\frac{1}{2}}$$

$$(16)$$

对于掺杂浓度一定的衬底硅片,由 $Q_s$ 可以计算出晶体硅表面电势 $\phi_s$ ,由于在非平衡条件下,电子和空穴的准费米能级 $(\phi_n \pi \phi_p)$ 都是非平衡载流子注入水平的函数。

由以上分析可知,晶体硅表面电势( $\phi_s$ )也是载流子注入水平( $\Delta n$ )的函数。且 $\phi_s$ 随着载流子注入水平( $\Delta n$ )的增加而逐渐减小,以至于在高注入水平条件下,晶体硅表面电势( $\phi_s$ )消失。这是由于高注入水平条件下有: $\Delta n > p_0$ , $n_0$ ,电子和空穴的准费米能级都回到了晶体硅禁带中央,从而 $|\phi_n| = |\phi_p|$ 。

### 2 实验结果及分析

#### 2.1 表面电势对 C-Si(N)硅片表面钝化的影响

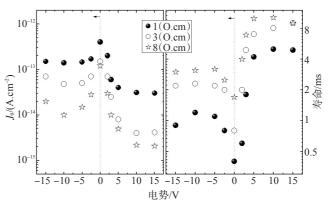

实验中电阻率分别为 1、3.5 和 10  $\Omega$ .cm的 C-Si (N)硅片上双面生长厚度为 105 nm的热氧化SiO<sub>2</sub>,然后在425 °C 条件 Forming Gas (N<sub>2</sub> + H<sub>2</sub>(5%~10%)) 环境退火 15 min。C-Si (N) 硅片两边表面施加 $-3 \times 10^{12}$  cm $^{-2} \rightarrow 3 \times 10^{12}$  cm $^{-2}$ 的表面电荷密度,少数

载流子寿命和表面饱和电流密度如图3所示。

图3 表面电势对C-Si(N)硅片表面钝化的影响

在SiO<sub>2</sub>/C - Si/SiO<sub>2</sub>结构表面施加正电势的条件下,以上三种不同电阻率的 C-Si(N)硅片有效少子寿命都有明显的改进。在最高电势条件下,硅片表面产生最小的表面饱和电流。当 C-Si(N)硅片表面电势逐渐增加,硅片表面形成电子聚集和空穴耗尽,从而降低界面复合速度,表面复合不会成为限制硅片表面有效少子寿命的主要因素,从而测试得到的有效少子寿命能非常接近 C-Si(N)硅片体寿命。

在SiO<sub>2</sub>/C - Si/SiO<sub>2</sub>结构表面施加负电势的条件下,和没有施加电势的条件相比,C-Si(N)硅片少数载流子寿命有一定程度的增加,但是施加正电势条件下得到的最大少子寿命要高于施加负电势条件下得到的最大少子寿命。C-Si(N)硅片表面的高密度负电荷在硅片表面产生空穴的聚集和电子耗尽。C-Si(N)硅片的主要杂质间隙铁原子对电子和空穴的俘获截面非常不对称,间隙铁原子对电子的俘获截面为: $6\times 10^{-14}$  cm²,其对电子的俘获截面近大于其对空穴的俘获截面 $\delta_n >> \delta_p$ ),从而从降低界面复合速度的角度来说,形成电子的聚集比形成空穴的聚集区域能更有效地降低界面复合速度。

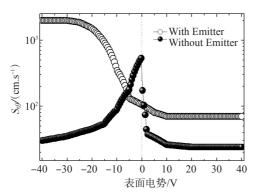

图 4 是表面有效复合速度  $S_{eff}$ 与表面电势和表面扩散发射结之间的实验数据拟合关系图。对于  $SiO_2/C-Si(n^+)/C-Si(p)$ 结构,其有效表面复合速度  $S_{eff}$ 包括表面复合和发射结内部复合。

对于 SiO<sub>2</sub>/C-Si(p)结构,在给定载流子注入水平条件下:(1)表面高密度正电荷相对于高密度负电荷能更有效地降低界面复合速度 $Q_f$ ;(2)高密度正电荷在载流子高注入水平下能更有效地降低界面有效复合速度;(3)负电荷覆盖的 SiO<sub>2</sub>/C-Si(p)结构,在电势约为-2~-3V 范围内出现有效复合速度的

图 4 表面电势与表面扩散发射结之间的关系

最大值,这正是由于缺陷态对电子/空穴俘获截面的 不对称性所导致的。

对于  $SiO_2/C-Si(n^+)/C-Si(p)$ 结构,在给定载流子注入水平条件下:(1)表面高密度正电荷在热氧化钝化的发射结表面能显著降低表面复合速度  $S_{eff}$ ;(2)表面高密度负电荷在  $SiO_2/C-Si(n^+)/C-Si(p)$ 结构表面没有表现出钝化效果,反而使有效复合速度提高一个数量级以上;(3)相对于  $SiO_2/C-Si(p)$ 结构, $SiO_2/C-Si(n^+)/C-Si(p)$ 结构不可能通过表面高密度负电荷来降低界面复合速度。

从图4中可以看出,对C-Si(p)结构表面施加高密度正电荷与高密度负电荷都能有效降低界面有效复合速度;但是对于C-Si(n+)/C-Si(p)结构表面,只有施加高密度正电荷才能有效降低界面复合速度,而施加高密度负电荷只能恶化界面复合质量。在C-Si(n)衬底表面施加正/负电势都能有效降低表面复合速度,且表面有效复合速度降低的程度与C-Si(n)电阻率的大小成反比关系,这与载流子俘获截面的不对称性有关,此外发射结掺杂浓度也是影响界面复合速度不容忽视的因素。

对于C-Si(n)衬底,其表面有效复合速度的最大值发生在表面电势为零处,而C-Si(p)衬底表面有效复合速度的最大值发生在电势为-2V左右。虽然其表面都有SiO2覆盖,且SiO2中缺陷对电子/空穴的俘获截面严重不对称,出现这个差异能否说明SiO2在C-Si(p)衬底上的钝化质量要优于C-Si(n),这有待更深入的研究。

#### 2.2 表面电势对 C-Si(P) 硅片表面钝化的影响

对掺杂浓度为 $1 \times 10^{16}$ cm<sup>-3</sup>的 C-Si(P), 假设硅片体内缺陷对电子和空穴有相同的俘获截面( $\delta_p = \delta_n$ )。当 C-Si(P)硅片表面施加密度为  $Q_s =$

$5 \times 10^{10} \, \mathrm{cm}^{-2}$ 的表面正电荷, $C - \mathrm{Si}(P)$ 硅片表面空穴浓度相对于电子浓度将会逐渐减小,随着表面正电荷的增加,硅片表面将会逐渐形成空穴的耗尽,甚至在 $C - \mathrm{Si}(P)$ 硅片表面产生反型层。当表面电子和空穴浓度相等时 $(p_s = n_s)$ , $C - \mathrm{Si}(P)$ 硅片表面有最大的复合速度产生。在高注人条件下,由于载流子注人浓度远高于掺杂浓度,晶体硅表面电势趋于形成平带。

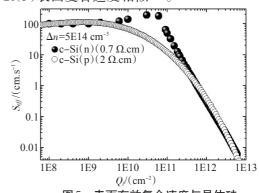

Girisch et al<sup>[11]</sup>根据 Shockley-Read-Hall 复合建 立了固定电荷密度和表面复合速度之间的关系。 根据图5中不同掺杂类型晶体硅,表面有效复合速 度与晶体硅表面固定负电荷密度之间的模拟关系 所示,在表面负固定电荷 $10^8 < Q_f < 10^{13}$  cm<sup>-2</sup>整个范 围内,C-Si(P)硅片表面复合速度随表面负电荷密 度的增加而降低; 当 $Q_f < 5 \times 10^{10} \text{ cm}^{-2} \text{时, C-Si(N)}$ 硅 片表面复合速度随负电荷密度的增加而增加;当  $Q_f > 5 \times 10^{10} \text{ cm}^{-2}$ 时, C-Si(P)硅片表面复合速度随 负电荷密度的增加而降低;  $\leq Q_f > 3 \times 10^{11}$  cm<sup>-2</sup>时, C-Si(P)和C-Si(N)硅片表面复合速度对表面电荷 的依赖相似。由于表面复合速度正比于表面少数 载流子浓度,当 $5 \times 10^{10} \text{ cm}^{-2} < Q_f < 1 \times 10^{13} \text{ cm}^{-2}$ 时, 对于C-Si(P)和C-Si(N)硅片表面来说电子始终是 少数载流子;  $\leq Q_f < 5 \times 10^{10} \text{ cm}^{-2} \text{ tf}, C-\text{Si}(N)$  硅片表 面复合速度的增加是由于空穴在这个条件下是少 数载流子,而且随着表面固定负电荷密度的增加, 空穴浓度增加进而导致了表面复合速度的增加。 对于富含正电荷的钝化介质,在C-Si(P)硅片也观 察到了以上相似的现象[10]。当 $Q_f > 5 \times 10^{11} \, \text{cm}^{-2}$ 时, C-Si(P)和 C-Si(N)硅片表面复合速度与 $1/Q_f^2$ 成正 比例下降关系,这一结果与Kuhlmann et al.报道的 C-Si(P)表面复合速度相似[12]。

图 5 表面有效复合速度与晶体硅 表面固定负电荷密度模拟关系

$Al_2O_3$ 薄膜能实现优良的场钝化效果 $^{[13-16]}$ ,由于 $Al_2O_3$ 薄膜中具有高密度 $(10^{11}~cm^{-2})$ 负电荷, $Al_2O_3$ 退火 $(30~min,425^{\circ}C~in~N_2$ 环境)后膜中固定负电荷密度能提高两个数量级到 $10^{12}\sim10^{13}~cm^{-2}$ 。且退火后  $Al_2O_3/C-Si$  界面态密度能降低超过一个数量级到  $1\times10^{11} eV^{-1} cm^{-2}$ 。而界面态密度的降低得益于  $Al_2O_3/C-Si$  界面出现的高质量的 $SiO_x(x>0)$ 层。同时 $Al_2O_3$ 薄膜中高密度的负电荷能更大程度的允许  $Al_2O_3/C-Si$  界面的高界面态密度,同时能保持一个比较高的钝化质量。

### 3 讨论

晶体硅表面钝化介质中固定电荷的极性对于 其在晶体硅表面的钝化质量非常重要。对于高效 晶体硅电池常用的钝化材料来说:热氧化SiO2、  $SiN_x(x>0)$ 以及非晶硅材料中都具有高密度的正电 荷 $(Q_f)$ ,它们在轻掺杂的C-Si(P)和C-Si(N)硅片 表面产生高质量的钝化效果[17-21]。对于高掺杂C-Si (P)硅片或发射结来说,其表面钝化介质的高密度正 电荷对其表面钝化来说是有不利的。这是因为高 密度正电荷会引起电子的聚集,从而导致表面复合 速率的增强;对于轻掺杂C-Si(P)硅片来说,具有高 密度表面正电荷的介质,其在C-Si(P)硅片表面的 钝化对载流子注入水平有着明显的依赖。在低注 入水平条件下,其表面钝化质量将会降低,从而这 对于在低注入水平条件(5×10<sup>14</sup>cm<sup>-3</sup>)下工作的晶体 硅电池来说是不利的。低注入水平条件下的这种 依赖关系归因于靠近界面晶体硅表面反型层内的 复合。对于富含负电荷的Al<sub>2</sub>O<sub>3</sub>薄膜来说,低注入水 平条件下,其优良钝化质量保持不变。用带负电的 Al<sub>2</sub>O<sub>3</sub>薄膜来钝化轻掺杂的C-Si(N)硅片表面,其钝 化质量对载流子注入水平有严重的依赖,低注入水 平条件下,其钝化质量将会降低。而表面富含高密 度正电的钝化介质的钝化质量将会保持不变。

高密度正电荷PECVD-SiN<sub>x</sub>(x>0)薄膜钝化C-Si(P)硅片电池背表面,将会产生寄生漏电流效应,严重降低电池的短路电流( $J_{sc}$ )。采用Al<sub>2</sub>O<sub>3</sub>材料来钝化C-Si(P)硅片电池的背面,不会产生这种漏电流效果,且采用Al<sub>2</sub>O<sub>3</sub>钝化的电池效率可达20.6%<sup>[4]</sup>。对于高掺杂C-Si(P)硅片表面,具有高密度负电荷的AL<sub>2</sub>O<sub>3</sub>薄膜其钝化效果要远优于表面带正电的钝

化介质材料(热氧化SiO<sub>2</sub>、SiN<sub>x</sub>(x > 0))。

### 4 结束语

分析了影响晶体硅界面钝化的主要界面态密度( $D_u$ )和晶体硅表面电荷,并讨论了它们随载流子注入水平变化对表面复合速度的影响程度。随着载流子注入水平的降低,富含正电荷(负电荷)的钝化介质在P型(N型)硅片上的钝化质量随之降低,而这部分界面钝化质量的降低主要是由靠近晶体硅表面反型层内的复合所导致;富含负电荷(正电荷)的钝化介质在P型(N型)硅片上的钝化质量却保持不变,这对于工作在低注入水平条件下( $5 \times 10^{14}$  cm<sup>-3</sup>)的晶体硅电池非常重要。通过深入分析P型(N型)掺杂硅片表面钝化质量随注入水平变化而产生不同变化的原因,能对高效晶体硅电池表面钝化提出指导性意见。

#### 参考文献

- [1] M A Green, F D King, J Shewchun. Minority carrier MIS tunnel diodes and their application to electron- and photo-voltaic energy conversion-I. Theory [J]. Solid-State Electronics, 1974, 17:551–561.

- [2] R R King, R A Sinton, R M Swanson. Doped surfaces in one sun, point-contact solar cells [J]. Applied Physics Letters, 1989,54(15):1460–1462.

- [3] P M Lenahan, T D Mishima, T N Fogarty, et al. Atomic-scale processes involved in long-term changes in the density of states distribution at the Si/SiO<sub>2</sub> interface [J]. Applied Physics Letters, 2001,79(20):3266–3268.

- [4] J Schmidt, A Merkle, R Brendel, et al. Surface passivation of high-efficiency silicon solar cells by atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub>[J]. Prog. Photovoltaics, 2008, 16: 461.

- [5] S M Sze. Semiconductor devices, physics and technology [M]. New York: Wiley , 1985.

- [6] S W Glunz, D Biro, S Rein, et al. Field-effect passivation of the SiO<sub>2</sub>-Si interface [J]. Journal of Applied Physics, 1999,86(1):683–691.

- [7] A G Aberle, S Glunz, W Warta. Impact of illumination level and oxide parameters on Shockley-Read-Hall recombination at the Si-SiO interface [J]. J. Appl. Phys., 1992,71:4422.

- [8] R Hezel, R Sch orner, T Meisel. Application of amorphous silicon nitride for MIS/inversion layer solar cells

- [C]//Proc 3rd EPVSEC, 1980: 866-870.

- [9] A S Grove, D J Fitzgerald. Surface effects on p-n junctions: Characteristics of surface space-charge regions under non-equilibrium conditions [J]. Solid-State Electronics, 1966, 9:783–806.

- [10] D J Fitzgerald, A S Grove. Surface recombination in semiconductors [J]. Surface Science, 1968,9(2):347– 369.

- [11] R B M Girisch, R P Mertens, R F De Keersmaecker. Determination of Si-SiO<sub>2</sub> interface recombination parameters using a gate-controlled point-junction diode under illumination [J]. IEEE Transactions on Electron Devices, 1988, 35(2);203–222.

- [12] B Kuhlmann, A G Aberle, R Hezel, Proceedings of the 13th European PVSEC [C]//UK: Nice, France Stephens Bredford, 1995:1209.

- [13] G Agostinelli, P Vitanov, Z Alexieva, et al. Surface passivation of silicon by means of negative charge dielectrics [C]//Proceedings of the 19th European Photovoltaic Solar Energy Conference. Paris, France, 2004: 132–134.

- [14] G Agostinelli, A Delabie, P Vitanov, et al. Very low surface recombination velocities on p-type silicon wafers passivated with a dielectric with fixed negative charge

[J]. Solar Energy Materials and Solar Cells, 2006, 90

- (18-19):3438-3443.

- [15] B Hoex, S B S Heil, E Langereis, et al. Ultra low sur face recombination of c-Si substrates passivated by plasma-assisted atomic layer deposited Al2O3[J]. Applied Physics Letters, 2006,89:042112.

- [16] R Hezel, K Jaeger. Low-Temperature Surface Passivation of Silicon for Solar Cells [J]. J. Electrochem, 1989, 136:518.

- [17] A G Aberle, S Glunz, W Warta. Impact of illumination level and oxide parameters on Shockley – Read – Hall recombination at the Si-SiO<sub>2</sub> interface[J]. J.Appl.Phys., 1992,71:4422.

- [18] R Hezel, R Schorner. Plasma Si Nitride—A promising dielectric to achieve high - quality silicon MIS/IL solar cells [J]. J. Appl. Phys., 1981, 52:3076.

- [19] I Martin, M Vetter, M Garin, et al. Crystalline silicon surface passivation with amorphous SiCx: H films deposited by plasma-enhanced chemical-vapor deposition [J]. J. Appl. Phys., 2005, 98:114912.

- [20] M J Kerr, A Cuevas. Recombination at the interface between silicon and stoichiometric plasma silicon nitride [J]. Semicond. Sci. Technol., 2002, 17:166.

- [21] M J Kerr, A Cuevas. Very low bulk and surface recombination in oxidized silicon wafers [J]. Semicond. Sci. Technol., 2002, 17:35.

#### (上接第23页)

不同温度下镜头传递函数曲线基本一致。综合分析以上结果,认为该系统在工作温度范围内实现了良好消热。

#### 3 结 论

从理论上分析探讨了温度变化对光学系统的 影响,并给出设计实例。通过消热差方程组的求解 获得多种初始结构和材料组合,在此基础上依据材 料选取原则进行取舍,使得温度变化时透镜热常量 导致的离焦正好和镜筒材料的热膨胀系数导致的 像面移动相一致,在一定温度范围内获得无热化光 学系统,镜头成像质量满足技术指标要求,装调后 的光学镜头已通过温度测试。

#### 参考文献

- [1] 李婕,张志明,冯生荣.弹载红外光学系统被动消热技术 [J].红外技术,2005(3):196-201.

- [2] 吴晓靖,孟军和.红外光学系统无热化设计的途径[J].红 外与激光工程,2003(6):6-11.

- [3] Hu Yuxi, Zhou Shaoxiang, Xiang Libin, et al. Design of athermal optical system[J]. Acta Optica Sinica, 2000, 20(10).

- [4] 冯生荣,李凯.红外光学系统的热效应[J].红外技术, 1990,12(2):6-11.

- [5] 刘健,郝云彩,常军,等.无热化星敏感器光学系统设计 [J].北京理工大学学报,2010(2):24-27.

- [6] Tamagaway Y, Tajime T. Dual-band optical system with a projective athermal chart: design [J].Appl Opt, 1997,36 (1):297–301.